7800X3D Tuning: PBO, UXTU (Universal x86 Tuning Utility) Workaround + Memory Optimization

I tuned a 7800X3D on a budget B650M-CW board, pushing it from stock performance to a realistic, daily-driver stable peak. The process combined per-core PBO offsets, structured manual testing, memory tuning, a UXTU workaround, and thermal control via Remoo Fan Control on a basic Thermaltake 240mm AIO.

Claude produced a .docx summary of the tuning process (linked separately), and I'm providing timing screenshots setting screen shots as well as a cheat sheet in comments.

System Overview

- CPU: AMD Ryzen 7 7800X3D (average bin)

- GPU: RX 9070 XT

- RAM: 32GB DDR5 Thermaltake Tough XG RGB — Hynix M-Die SR (EXPO 36-38-38-78, CL36 kit)

- Motherboard: ASRock B650M-CW | BIOS 3.50 | AGESA ComboAM5PI 1.2.0.3g

- Cooler: Thermaltake 240mm AIO

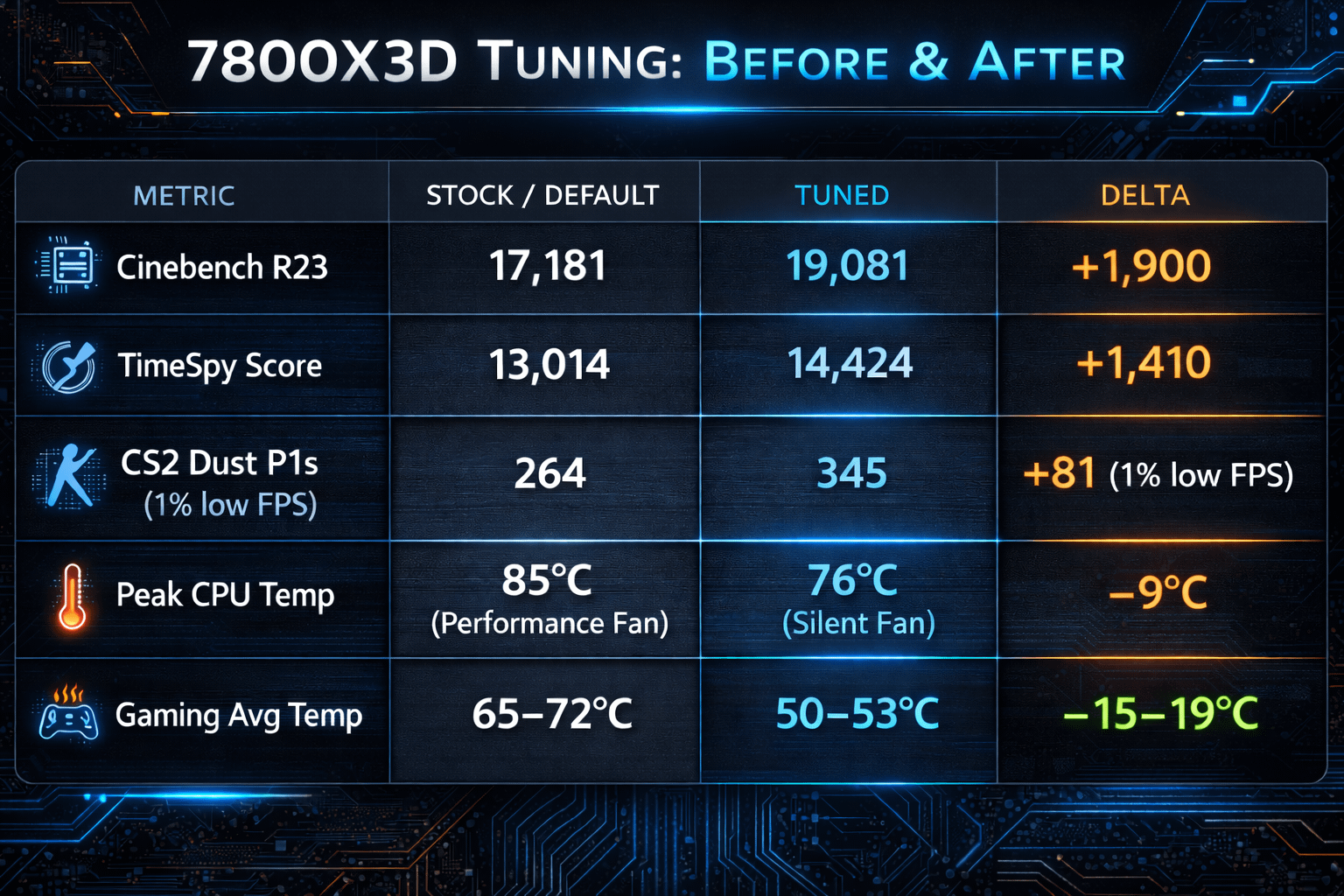

Starting Stock Performance (EXPO Enabled)

- Cinebench R23: 17,181

- 3DMark TimeSpy Total: 13,014

- CS2 Dust P1s 1% Low FPS: 264

- Peak CPU Temp: 85°C

- Gaming Avg CPU Temp: 65–72°C

- AIDA64 Latency: ~80 ns

Final Performance Summary

- Cinebench R23: 17,181 → 19,081 (+1,900)

- TimeSpy: 13,014 → 14,424 (+1,410)

- CS2 Dust P1s 1% Low FPS: 264 → 345 (+81)

- Peak CPU Temp: 85°C → 76°C (-9°C)

- Gaming Avg CPU Temp: 65–72°C → 50–53°C (-15–19°C)

- AIDA64 Latency: ~80 ns → 60–61 ns

Memory stabilized at 48°C during long stress tests and never exceeded 52°C.

Tuning Methodology

BZ Baseline & Community Research

I started from the BZ baseline and collated posts, comments, and videos from Reddit, YouTube, and overclocking forums to build a structured BIOS profile.

Research focused on:

- Hynix M-die tRFC scaling

- tRC correction theory (tRC < tRCD + tRP creates hidden IMC overhead)

- AM5 IMC voltage sensitivity

- Fabric synchronization and DF-C state behavior

This was done to avoid guessing and instead apply a formulaic approach.

Per-Core PBO Cycling (No Guessing)

I used traditional one-core-at-a-time PBO cycling.

Process:

- OCCT core cycling with 10-second windows per core

- HWiNFO logging to monitor per-core clock behavior

- Identify which cores failed to sustain 4500+ MHz during their solo window

- Adjust Curve Optimizer offset by 1 step after crashes

- Re-test immediately

Core5 was the weakest silicon:

- Pinned at 3233 MHz at CO -27

- Across 29 logged sessions it averaged 86 MHz below every other core

- Ranked last in 7 of 29 runs

Loosening Core5 to CO -23 completely stabilized it.

Core4 then exposed instability at CO -21 only after Core5 was corrected.

Final CO offsets:

- C0: -30

- C1: -28

- C2: -26

- C3: -22

- C4: -21

- C5: -23

- C6: -26

- C7: -26

TimeSpy graphs initially looked unstable under load even after traditional CO tuning. Logs from HWiNFO, TimeSpy, and OCCT single-core runs were used strictly for observation and validation. Every adjustment was manually tested.

AI Usage Clarification

AI was not used to “auto tune.”

It was used only to:

- Read HWiNFO logs

- Help identify weak cores via clock deltas

- Suggest tightening or loosening memory timings one step at a time

All changes were applied manually, one variable at a time, with CMOS resets and retesting across days/weeks.

Memory Tuning (Hynix M-Die CL36 Kit)

Default:

- EXPO 36-38-38-78

- AIDA latency ~80 ns

Final:

- DDR5-6000

- FCLK 2000 MHz

- UCLK = MCLK

- AIDA64 latency: 60–61 ns

Key voltage stack:

- VSOC 1.275V Fixed Mode with LLC2 (reads 1.265V in Zen Timings)

- VDDP 1.150V

- VDD Misc 1.100V

- VDDIO/VDD/VDDQ 1.440V

- SoC/Uncore OC Mode: Enabled

The slight VSOC droop via LLC2 appeared to help IMC boost consistency during all-core workloads. This range was extensively tested on this board and chip.

tRFC was scaled properly to MCLK (160ns × MCLK GHz principle).

tRC corrected to avoid hidden IMC overhead.

EXPO was not blindly trusted.

UXTU Workaround

BIOS PPT limits were hard-locking the CPU at 0.5 GHz.

UXTU (Universal x86 Tuning Utility) was used strictly to modify:

- PPT

- TDC

- EDC

Combined with ECO Mode 65W, this stabilized all-core clocks under load and eliminated TimeSpy instability.

Important note:

Windows Defender may silently quarantine UXTU after updates. When that happens, CS2 P1 can drop from 345 to ~305–316. Add a Defender exclusion for the UXTU directory.

Stability Stack (In Order)

- OCCT core cycling (10s per core) with logging

- OCCT all-core (AVX512 coherency)

- y-Cruncher VT3 90 min (AVX512 + VSOC/IMC stress)

- TM5 8-hour Ryzen X3D configuration

- Real-world CS2 Dust P1s testing

Fan Management

Remoo Fan Control was used to create silent curves.

BIOS fan profiles were set to Performance Mode as a fallback in case software control failed during real-time benchmarking.

Fan Step Down: 25 seconds to prevent oscillation.

The Thermaltake 240mm AIO maintained:

- 76°C peak under load

- 50–53°C average while gaming

Key BIOS Changes & Rationale

CPU & Boost

- Precision Boost Overdrive: Advanced

- CPPC Dynamic Preferred Cores: Frequency

- ECO Mode: 65W

- Core CO offsets per above

These allow strong cores to boost higher while weak cores are stabilized.

Fabric & Memory

- DDR5-6000

- FCLK 2000 MHz

- UCLK = MCLK

- DF-C States: Enabled

- Global C-State Control: Disabled

- ACPI _CST C1: Disabled

- Memory Context Restore: Disabled

- Power Down Enable: Disabled

DF-C was critical for DDR5-6000 stability. Disabling it previously caused instability.

Voltage & Power Delivery

- SoC Voltage: Fixed Mode

- VSOC 1.275V LLC2 (1.265V effective)

- VDDP 1.150V

- VDD Misc 1.100V

- VDDIO/VDD/VDDQ 1.440V

- SoC/Uncore OC Mode: Enabled

Misc / Security / Compatibility

- AMD CPU FTPM: Disabled (removes firmware overhead)

- WAN Radio: Disabled

- IOMMU: Disabled (reduces latency)

- SVM: Disabled

- SMEE / TSME: Disabled (removes encryption overhead)

- PCIe ARI Enumeration: Auto

- FCH Spread Spectrum: Disabled

- REP-MOV/STOS Streaming: Enabled

- Enhanced REP MOVSB/STOSB: Enabled

- Advanced Error Reporting: Not Supported

- dGPU Only Mode: Enabled

- Auto Driver Installer: Disabled

These changes collectively reduce background overhead, power gating, and frequency modulation that interfere with sustained boosting.

Key Takeaways

- An average-bin 7800X3D can reach realistic peak performance with disciplined per-core CO tuning.

- Core cycling with clock verification reveals weak cores — not guesswork.

- tRC and tRFC tuning matter more than most expect on Hynix M-Die.

- VSOC tuning with controlled droop helped IMC boost stability.

- UXTU + ECO Mode is essential on ASRock B650M-CW boards with PPT lock behavior.

- DF-C and C-State configuration are critical for DDR5-6000 stability.

- Logs were observational; every adjustment was manually validated.

- Memory stabilized at 48°C and never exceeded 52°C during extended stress.

TL;DR

- Per-core CO tuning with validated offsets

- VSOC 1.275V LLC2 (1.265V effective)

- DDR5-6000 Hynix M-Die CL36 tuned to 60–61 ns latency

- UXTU PPT/TDC/EDC workaround for BIOS lock

- Cinebench +1,900

- TimeSpy +1,410

- CS2 Dust P1s 1% Low +81

- CPU peak temp -9°C

- Gaming CPU temp -15–19°C

- Memory stable under 52°C